Analyst(s): Brendan Burke, Guy Currier

Publication Date: April 22, 2026

What is Covered in This Article:

- Cadence launches ViraStack and InnoStack AI Super Agents at CadenceLIVE 2026, extending an end-to-end agentic AI chip design flow from spec to signoff, with early customers reporting 3–10x productivity gains

- Cadence’s customer-driven product development model: agents are tested with lead customers and incrementally extended on ChipStack’s Mental Model foundation before production release — a deliberate contrast to the “ship and hope” approach seen elsewhere in enterprise AI

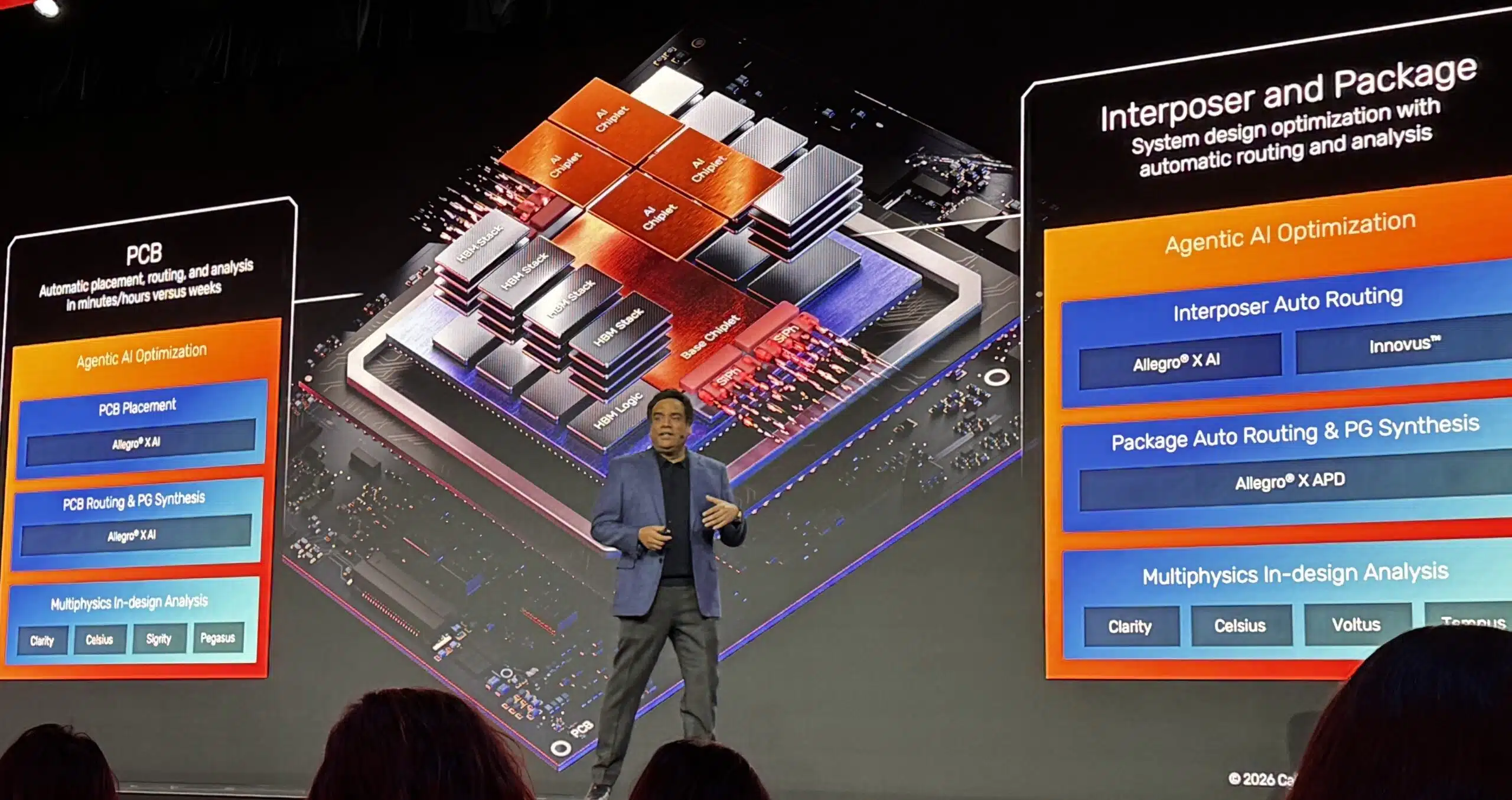

- CEO Anirudh Devgan calls out 3D IC signoff as a critical customer pain point and positions GPU-accelerated Millennium and Allegro X AI as the packaging automation answer

- Why 3D IC design automation remains the industry’s most stubborn gap — still overwhelmingly manual, with no single vendor offering a production-ready automated path — and how Jensen Huang’s observation that verification requires 100x the engineering of design only gets worse in multi-die packages

- How Cadence’s Allegro X AI and GPU-accelerated Millennium platform position the company for advanced packaging automation, even as the full agentic solution remains on the horizon

The Event — Major Themes & Vendor Moves: CadenceLIVE Silicon Valley 2026, held April 15–16 at the Santa Clara Convention Center, is Cadence Design Systems’ flagship annual user conference, drawing chip designers, systems engineers, and EDA ecosystem leaders for two days of technical sessions and product announcements.

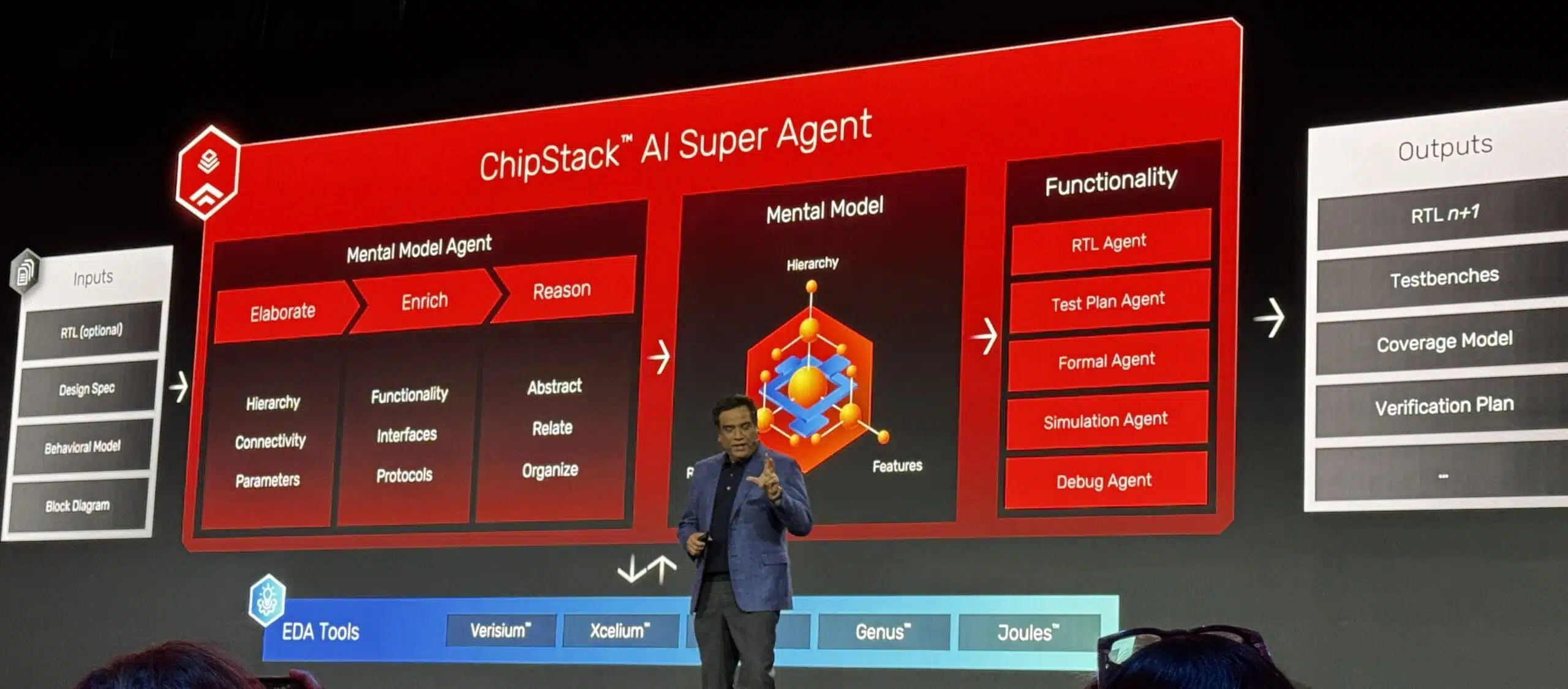

The event featured over 50 sessions spanning digital design, analog, verification, system design, and physical AI. The defining narrative at CadenceLIVE 2026 was the expansion of Cadence’s agentic AI ambition beyond front-end RTL and verification into the full chip design stack. CEO Anirudh Devgan used his Visionary Address to unveil two new AI Super Agents — ViraStack for analog design and migration, and InnoStack for digital back-end implementation and signoff — alongside the new AgentStack orchestration environment that ties them together with the previously launched ChipStack AI Super Agent. Cadence refers to domain-specific agentic systems as Super Agents, each scoped to a phase of the design flow and orchestrated by AgentStack: a governed, multi-agent orchestration system.

Together, these create what Cadence claims is the industry’s first end-to-end agentic AI chip design flow, from specification through signoff. Devgan framed the urgency in stark terms: the semiconductor industry, once projected to reach $1 trillion by 2030, is now expected to hit that figure in 2026 itself, with latest projections from Bank of America pushing estimates to $1.3 trillion this year and $2 trillion by 2030. One major hyperscaler told Devgan that every new AI chip iteration requires 2x more engineers — a pace that is flatly unsustainable. This engineering labor crisis is the demand signal behind Cadence’s agentic bet.

This represents a demand shock in the custom silicon market. Within the past year, both the cost and time required for custom chip design and multi-die integration have fallen below a certain threshold, one at which system architects are beginning to incorporate custom silicon into their roadmaps by default rather than exception. The silicon engineering labor force cannot scale at this pace; Cadence’s agentic AI bet is fundamentally a supply-multiplier argument.

Equally notable was Devgan’s pointed commentary on 3D IC signoff as one of the most acute customer pain points. With HBM stacks reaching 12–16 layers and multi-die packages introducing compounding thermal, IR drop, and stress analysis challenges, Devgan positioned Cadence’s GPU-accelerated Millennium platform and Allegro X AI as the foundation for bringing digital-design-class automation to advanced packaging for the first time. The expanded NVIDIA partnership, reinforced at CadenceLIVE after its GTC 2026 announcement, combines Cadence’s agentic EDA tools with NVIDIA CUDA-X, AI physics, and Omniverse to accelerate GPU-native chip and system design. A parallel Google Cloud collaboration integrates ChipStack with Gemini foundation models.

Cadence Agentic AI Reaches the Full Stack, But 3D IC Is Where the Real Test Begins

Analyst Take: At CadenceLIVE 2026, Cadence completed the most ambitious agentic AI product launch in EDA history: three domain-specific AI Super Agents — ChipStack for front-end RTL and verification, ViraStack for analog design, and InnoStack for digital back-end and signoff — unified under a new AgentStack orchestration layer. Early customers are reporting 3–10x productivity improvements with ViraStack in analog design workflows, and Cadence claims up to 10X gains from ChipStack in front-end design. These are attention-grabbing numbers.

Justifying this strategy, Cadence asserted that EDA has been a reasoning system almost from its outset. Synthesis, place-and-route, and formal verification are fundamentally optimization and proof engines. What LLMs and agentic AI do is add orchestration, natural-language interaction, and knowledge-capture layers to improve efficiency and speed. Cadence’s Mental Model architecture grounds agent actions in existing EDA tool constraints rather than allowing LLM-generated suggestions to operate unchecked. Chip design teams can expect dramatic workflow productivity gains without the risk of the underlying solver engines changing.

But an equally important story to watch from CadenceLIVE was the problem Devgan said agents cannot yet fully solve: 3D IC design automation. Devgan called out 3D IC signoff as a major pain point in his keynote, and for good reason. When HBM stacks hit 12 or 16 layers, when multi-chiplet packages introduce compounding thermal gradients and voltage integrity issues across die-to-die interfaces, the signoff problem explodes in dimensionality. As Futurum’s own research on advanced packaging for AI semiconductors has documented, the industry is rapidly moving toward 2.5D and 3D integration, but the design and verification tool ecosystem has not kept pace with the manufacturing ambition. This is still overwhelmingly manual work, and there is no single vendor today that can take a 3D IC design from concept through signoff in a production-ready automated flow.

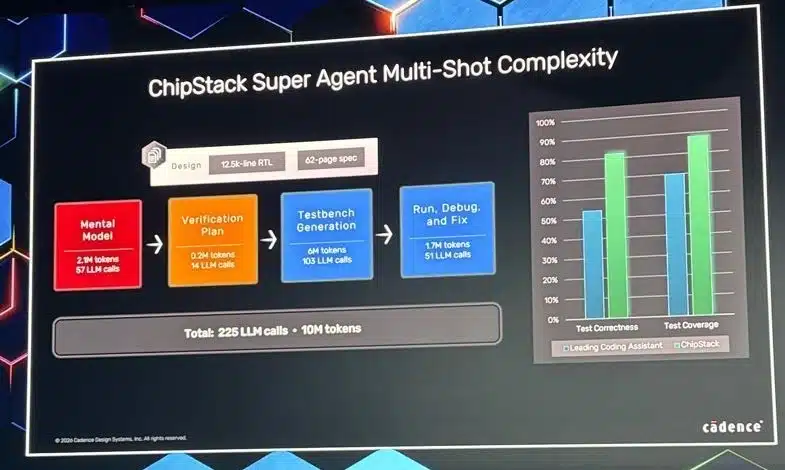

ViraStack and InnoStack Launch Signal a Customer-Driven Approach

What distinguishes Cadence’s agentic AI rollout from the “agent washing” that pervades the broader enterprise software market is the customer co-development model underpinning the product roadmap. Cadence is not shipping agents and hoping they work. ChipStack was acquired in November 2025, launched in February 2026, and has been tested in production with lead customers — including NVIDIA, MediaTek, Google, Qualcomm, and Broadcom — before features are expanded. Our briefing with Kartik Hegde, Senior Group Director for Agentic AI and ChipStack, shared that Cadence measures agent quality across three dimensions: test correctness (are assumptions about the design valid?), test coverage (is every feature exercised?), and bug injection catch ratio (if a random bug is inserted, does the agent find it?). This enables formal verification of agentic steps that demonstrate readiness for deployment.

ViraStack and InnoStack follow the same pattern: initial capabilities are being co-validated with design teams at these companies before broader release. This incremental, test-before-you-ship approach matters because the consequences of agent failure in chip design are qualitatively different from those of a bad customer service chatbot response. A verification escape or a back-end optimization error can mean a multi-million-dollar respin. Cadence’s Mental Model — the intermediate knowledge representation that grounds agent behavior in principled EDA tool boundaries rather than raw LLM hallucination — was originally developed for ChipStack and is now the architectural foundation for ViraStack and InnoStack as well. Skills and scaffolding are added incrementally as customers validate correctness in real production contexts.

3D IC Automation: The Industry’s Most Stubborn Gap

Cadence’s agentic AI strategy is impressive, but it is solving the problems that were already on the automation roadmap. RTL generation, verification closure, analog migration, back-end floorplanning — these are high-value, high-labor workflows that were always going to be the first targets for AI augmentation. The harder, more important problem is 3D IC, and that is where Cadence’s story gets more honest and more tentative. Jensen Huang has noted that verification alone can require 100X the engineering effort of design. In a 3D IC context, that ratio gets worse, not better, because multi-die verification introduces cross-die timing, thermal coupling, and power integrity interdependencies that monolithic design flows were never built to handle.

Cadence’s Allegro X platform is the leading advanced packaging design tool, and with Allegro X AI, the company is bringing placement, routing, and early agentic flow automation to packaging and PCB. But Devgan was candid in his keynote: the roadmap for a full 3D IC design agent and multi-physics signoff agent is still pending customer co-design and testing. That work has not shipped. Futurum Intelligence’s 1H 2026 AI Platforms decision-maker survey shows that R&D and engineering ranks as the third most likely deployment area for agentic AI, cited by 39.6% of enterprises — trailing only IT operations/cybersecurity (49.2%) and customer experience (48.6%).

Millennium and Allegro X AI: The 3D IC Acceleration Play

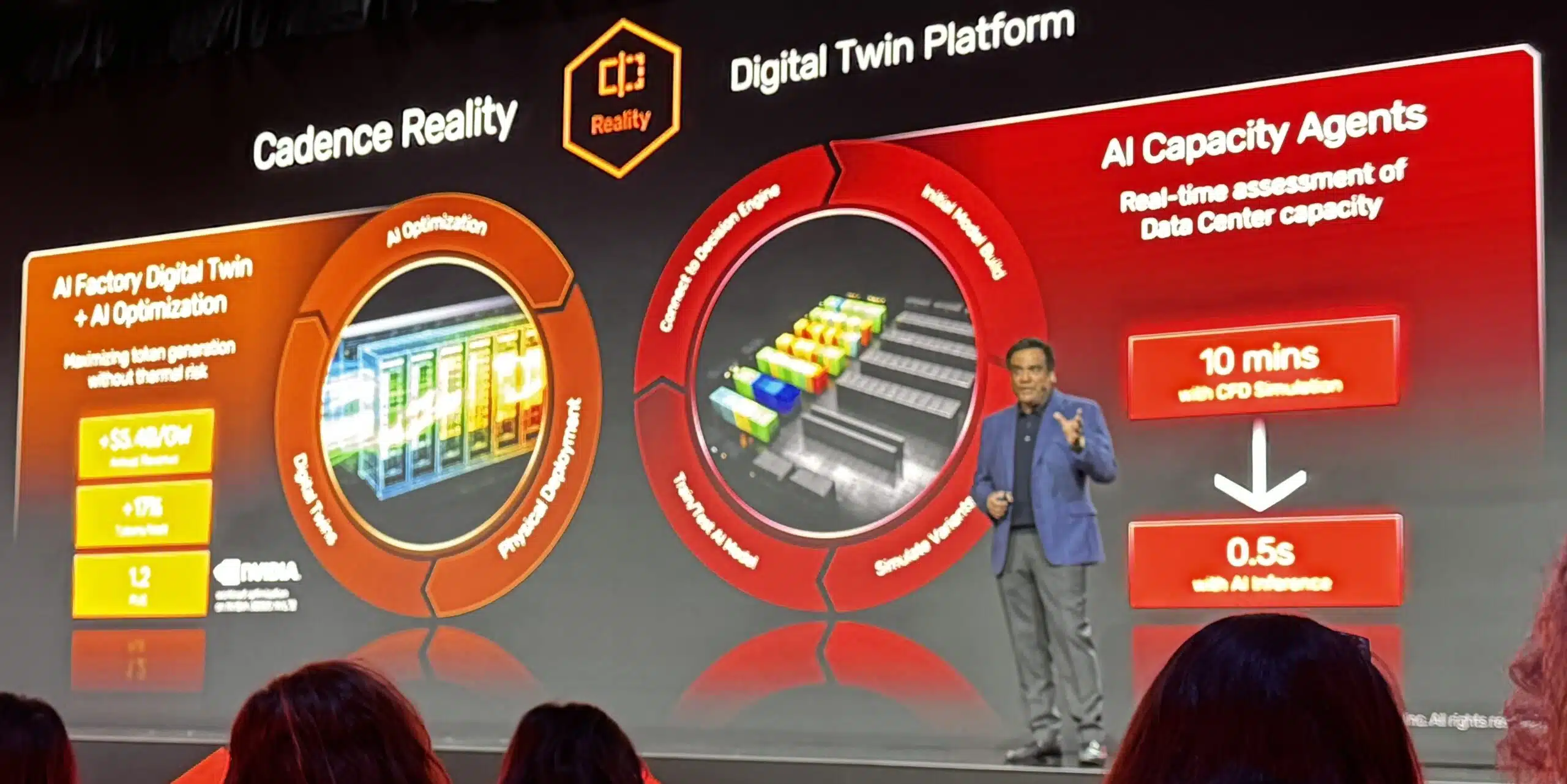

Cadence’s strongest near-term answer to the 3D IC challenge is not purely agentic — it is computational. The Millennium platform, which accelerates numerical EDA workloads on GPUs, is being extended from circuit simulation (Spectre) and CFD (Cascade) into 3D IC signoff: voltage IR drop, power integrity, thermal analysis, and stress simulation across multi-chiplet packages. Devgan described this as “ideal for Millennium” because the underlying computations are heavy matrix multiply operations that GPUs excel at. Combined with Allegro X AI’s emerging automation capabilities for advanced packaging layout, this creates a two-pronged approach: GPU-accelerated compute to make 3D signoff fast enough to be practical, and early AI-assisted automation to reduce manual effort in packaging design.

The missing piece — and the piece Cadence was transparent about — is the full agentic orchestration layer for 3D IC. A future where an AI Super Agent autonomously manages multi-die floorplanning, cross-die verification, thermal-aware placement, and signoff closure is the logical extension of what ChipStack, ViraStack, and InnoStack are doing for monolithic chip design. But that future requires solving multi-physics simulation coupling in an agent loop, which is a fundamentally harder problem than single-domain optimization. Synopsys, with its Ansys acquisition and multi-physics design strategy unveiled at Converge 2026, is pursuing the same frontier from a simulation-first angle.

From Chip to Chiller: The Longer Arc

Our briefing with Rob Knoth, Senior Group Director of Strategy and New Ventures, hinted at a longer-term vision he called “chip to chiller” — the idea that Cadence’s combined EDA, packaging, and system-level simulation tools could eventually optimize from silicon architecture through data center thermal management. The Cadence Reality Digital Twin Platform was presented as a production-ready solution to boost tokenization and revenue per watt through cooling optimization. With the Future Facilities acquisition (data center digital twins), Cascade (GPU-accelerated CFD), and now agentic orchestration, the pieces are assembling. The AgentStack head-agent architecture, designed to add new domain-specific super agents into an existing orchestration hierarchy, is the structural enabler for this cross-domain ambition.

What to Watch:

- 3D IC design agent timeline: Track whether Cadence can ship production-ready 3D IC agentic capabilities by CadenceLIVE 2027 — that timeline will determine whether the company leads or follows in the most critical EDA growth segment.

- Synopsys multi-physics counter-strategy: Synopsys’ Converge 2026 event laid out a competing vision for multi-physics 3D IC design built on the Ansys integration, including the AgentEngineer L4 multi-agent design system. Watch for whether Synopsys ships a 3D IC-specific agentic agent before Cadence. The Ansys simulation depth could give it an edge in coupled thermal-electrical-mechanical signoff.

- Customer validation beyond demos: CadenceLIVE showed compelling metrics — ViraStack’s 3–10X analog speedups, ChipStack’s bug injection catch rates, and formal verification reduced from days to hours. The real proof will be production silicon designed with these agents.

- System designers and IT architects alike can keep pressing the gas on silicon and system diversity to achieve more, better with AI, HPC, and analytics workloads, among many others. Interoperability across multi-die packages, standardized chiplet interfaces (UCIe), and transparent signoff methodologies will be critical here.

- Self-evolving agents on the horizon: agents that improve autonomously from their own experience could dramatically accelerate the pace at which new domains become tractable for agentic automation.

- Quality over productivity as the value proposition: If the industry’s measurement framework shifts from “how fast” to “how right,” Cadence’s testing-and-trust approach becomes a decisive advantage.

Disclosure: Futurum is a research and advisory firm that engages or has engaged in research, analysis, and advisory services with many technology companies, including those mentioned in this article. The author does not hold any equity positions with any company mentioned in this article.

Analysis and opinions expressed herein are specific to the analyst individually and data and other information that might have been provided for validation, not those of Futurum as a whole.

Other Insights from Futurum:

Can Cadence Shorten Chip Design Timelines with ChipStack AI?

Synopsys Converge – Is the New Synopsys Ready to Own Multi-Physics Design?

Cadence Q4 FY 2025 Earnings Underscore AI-Led EDA Momentum