Analyst(s): Brendan Burke

Publication Date: January 27, 2026

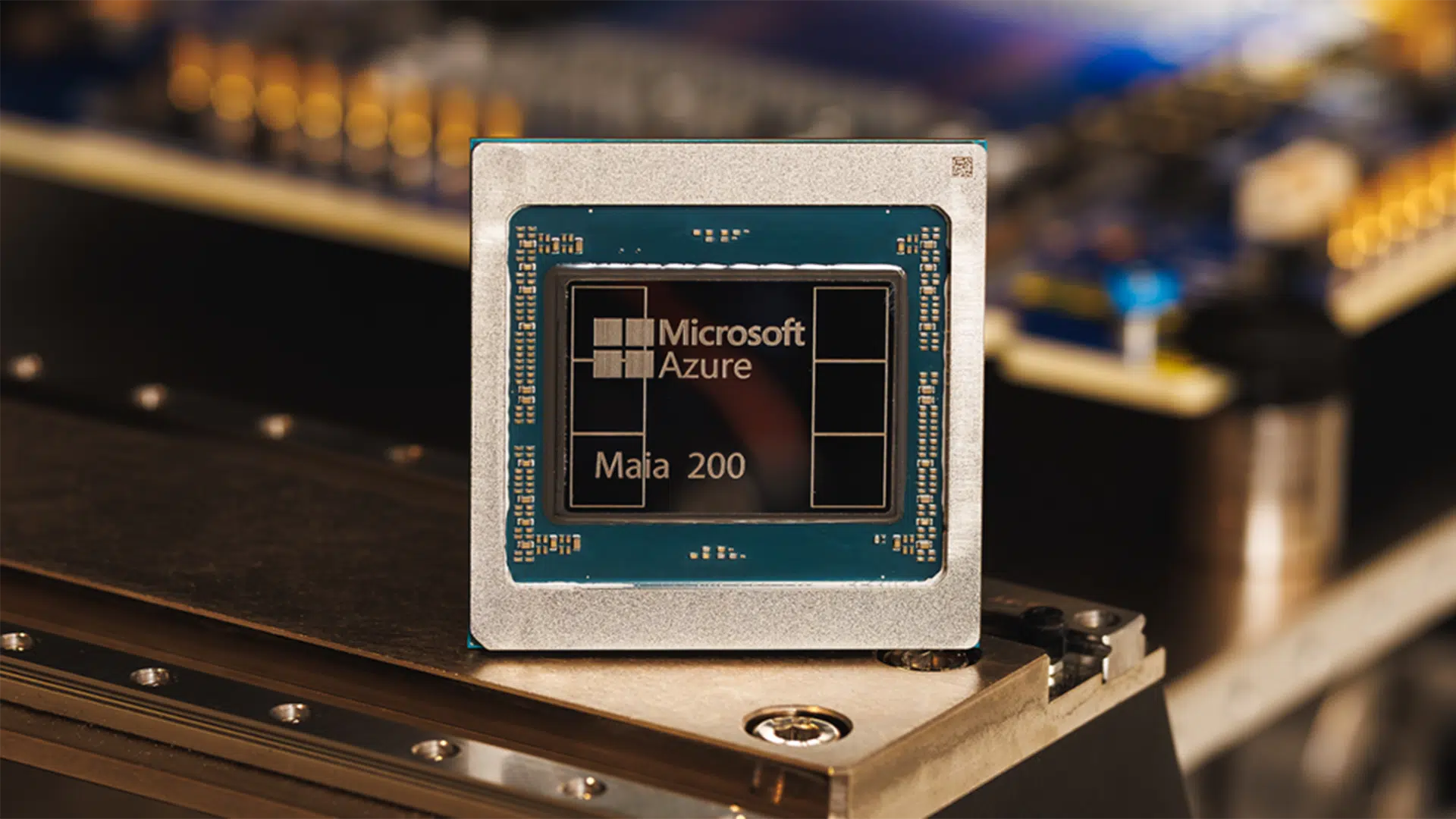

Microsoft introduced Maia 200, a 3nm, low‑precision AI inference accelerator with FP4/FP8 tensor cores, 216GB HBM3e at 7 TB/s, 272MB on‑die SRAM, and an Ethernet‑based two‑tier scale‑up network. Microsoft positions Maia 200 as its most performant first‑party silicon, designed to lower cost‑per‑token for inference while accelerating synthetic data generation and reinforcement learning (RL) pipelines for next‑gen models.

What is Covered in this Article:

- Key takeaways from the Maia 200 announcement

- Where Maia 200 fits in the XPU landscape

- Why reinforcement learning is the next battleground for specialized accelerators

The News: Microsoft announced Maia 200, a first‑party inference accelerator built on TSMC 3nm with native FP8/FP4 tensor cores, 216GB HBM3e delivering 7 TB/s bandwidth, and 272MB on‑die SRAM. The design emphasizes narrow‑precision compute, specialized DMA engines, and a high‑bandwidth NoC to increase token throughput and model utilization. Maia 200 will serve multiple models, including OpenAI’s GPT‑5.2, and support Microsoft Foundry, Microsoft 365 Copilot, and the Microsoft Superintelligence team’s synthetic data and reinforcement learning workflows.

At the systems level, Microsoft highlighted a two‑tier, Ethernet‑based scale‑up network with a custom transport layer, providing 2.8 TB/s of bidirectional dedicated scale‑up bandwidth per accelerator and collective operations scaling to clusters of 6,144 accelerators. Maia 200 is in production in the US Central region (Iowa), with US West 3 (Arizona) next, plus a preview Maia SDK offering PyTorch integration, a Triton compiler, optimized kernels, a low‑level language (NPL), and a simulator/cost model to tune workloads before deployment.

Microsoft’s Maia 200 Signals the XPU Shift Toward Reinforcement Learning

Analyst Take — XPU Market Context: For hyperscalers, silicon diversity matters for optimization of internal AI workloads. Maia 200 is squarely aimed at CEO Satya Nadella’s north-star metric, tokens-per-dollar-per-watt. The accelerator shines in mixed-precision, bursty inference and reinforcement learning (RL) workloads while reducing dependency on general-purpose GPUs. Microsoft has been highly strategic about balancing AI ambition with capital discipline. The chip is evidence of a deliberate strategy to align first-party silicon tightly with Microsoft’s own consumption patterns, rather than chasing external benchmarks for their own sake.

The XPU market reached $31B in 2025, according to Futurum’s research, including data center revenue from third-party custom silicon design firms. Third-party XPU design is a high-growth market that we believe could double by 2028. Maia 200 should be viewed as a Microsoft-architected system-on-chip, with partners including GUC, Marvell, and TSMC enabling scale economics that would be difficult to achieve in-house alone. TSMC’s capacity puts limits on the scale and timelines of this effort.

Why Reinforcement Learning is a Logical Target

Reinforcement learning and synthetic data generation are rapidly becoming the dominant marginal consumers of compute in frontier AI systems, especially as models evolve toward agentic behavior. These workloads stress systems differently from pretraining or static inference. They are simultaneously bandwidth-intensive (policy evaluation, reward model passes, filtering), latency-sensitive (rollouts, sampling, reward scoring), and economically unforgiving due to extremely high iteration counts.

Maia 200 is explicitly shaped around these characteristics. Its native FP4/FP8 tensor cores favor throughput over numerical excess, while 216GB of HBM3e and 272MB of on-die SRAM reduce external memory traffic during tight RL loops. Specialized data-movement engines further minimize overhead in control-flow-heavy pipelines. When paired with a deterministic Ethernet-based collective fabric, the result is a platform optimized for predictable iteration speed and low tail latency—exactly where RL and synthetic data pipelines tend to bottleneck.

Why Ethernet Networking is Notable

By extending standard Ethernet beyond scale-out and into scale-up with a custom transport layer, Microsoft is making a systems-level bet that cost structure and operational uniformity will outweigh the advantages of proprietary fabrics. Networking has emerged as a significant constraint in AI clusters. Ethernet’s emerging standards and low costs offer meaningful advantages at hyperscale. Although Maia 200 uses standard Ethernet signaling, its scale-up fabric avoids traditional multi-hop switched behavior, instead relying on deterministic, scheduled collectives optimized for tightly coupled accelerator clusters. This resembles the TPU’s deterministic fabric, enabling Microsoft to coordinate a large world size of 6,144 processors for custom model development.

Competitive Quantization

Industry momentum is shifting inference to lower precision to cut TCO while sustaining accuracy with quantization‑aware workflows. Maia’s native FP4/FP8 aligns with the broader AI engineering trend toward aggressive quantization for LLM inference and RL phases, where end‑to‑end pipeline accuracy can be maintained with careful calibration. Microsoft positions Maia 200 as exceeding Google’s latest TPU in FP8 and tripling the FP4 performance of Amazon Trainium 3, while delivering 30% better performance per dollar than Microsoft’s latest fleet generation. For workloads dominated by sampling, ranking, and reward evaluation, narrow precision delivers disproportionate economic benefit, yet may limit the performance of frontier pre-training workloads.

What to Watch:

- Real‑world performance: Signal65 testing will show how Maia 200 performs compared to common accelerators on high-value workloads.

- RL and synthetic data pipelines: Evidence that Maia 200 lowers costs for high-value Azure workloads, such as agentic reinforcement fine-tuning in Azure Foundry Agent Service.

- Microsoft Superintelligence model releases: the degree to which RL becomes visible in Microsoft’s model narratives will be an early proxy for how central Maia-class XPUs are to its long-term AI roadmap,

- Validation of the Ethernet-based scale-up fabric at ~6,000-accelerator world size, with particular focus on congestion avoidance without cascading performance collapse.

See the complete announcement of Maia 200 on the Microsoft Blog.

Disclosure: Futurum is a research and advisory firm that engages or has engaged in research, analysis, and advisory services with many technology companies, including those mentioned in this article. The author does not hold any equity positions with any company mentioned in this article.

Analysis and opinions expressed herein are specific to the analyst individually and data and other information that might have been provided for validation, not those of Futurum as a whole.

Other insights from Futurum:

GPU Alternatives Poised to Outgrow GPUs in 2026

Will Microsoft’s “Frontier Firms” Serve as Models for AI Utilization?

Is Tesla’s Multi-Foundry Strategy the Blueprint for Record AI Chip Volumes?

Image Credit: Microsoft

Author Information

Brendan is Research Director, Semiconductors, Supply Chain, and Emerging Tech. He advises clients on strategic initiatives and leads the Futurum Semiconductors Practice. He is an experienced tech industry analyst who has guided tech leaders in identifying market opportunities spanning edge processors, generative AI applications, and hyperscale data centers.

Before joining Futurum, Brendan consulted with global AI leaders and served as a Senior Analyst in Emerging Technology Research at PitchBook. At PitchBook, he developed market intelligence tools for AI, highlighted by one of the industry’s most comprehensive AI semiconductor market landscapes encompassing both public and private companies. He has advised Fortune 100 tech giants, growth-stage innovators, global investors, and leading market research firms. Before PitchBook, he led research teams in tech investment banking and market research.

Brendan is based in Seattle, Washington. He has a Bachelor of Arts Degree from Amherst College.